**Instruction Set**

### Instruction Set Nomenclature:

### Status Register (SREG):

- SREG: Status register

- C: Carry flag in status register

- Z: Zero flag in status register

- N: Negative flag in status register

- V: Twos complement overflow indicator

- S:  $N \oplus V$ , For signed tests

- H: Half Carry flag in the status register

- T: Transfer bit used by BLD and BST instructions

- I: Global interrupt enable/disable flag

#### Registers and operands:

- Rd: Destination (and source) register in the register file

- Rr: Source register in the register file

- R: Result after instruction is executed

- K: Constant literal or byte data (8 bit)

- k: Constant address data for program counter

- b: Bit in the register file or I/O register (3 bit)

- s: Bit in the status register (3 bit)

- X,Y,Z: Indirect address register (X=R27:R26,

- Y=R29:R28 and Z=R31:R30)

- P: I/O port address

- q: Displacement for direct addressing (6 bit)

### I/O Registers

RAMPX, RAMPY, RAMPZ: Registers concatenated with the X, Y and Z registers enabling indirect addressing of the whole SRAM area on MCUs with more than 64K bytes SRAM.

### Stack:

STACK:Stack for return address and pushed registers SP: Stack Pointer to STACK

#### <u>Flags:</u>

- $\Leftrightarrow$ : Flag affected by instruction

- 0: Flag cleared by instruction

- 1: Flag set by instruction

- -: Flag not affected by instruction

| Test         | Boolean       | Mnemonic  | Complementary | Boolean       | Mnemonic  | Comment  |

|--------------|---------------|-----------|---------------|---------------|-----------|----------|

| Rd > Rr      | Z•(N ⊕ V) = 0 | BRLT*     | Rd ≤ Rr       | Z+(N ⊕ V) = 1 | BRGE*     | Signed   |

| $Rd \ge Rr$  | (N ⊕ V) = 0   | BRGE      | Rd < Rr       | (N ⊕ V) = 1   | BRLT      | Signed   |

| Rd = Rr      | Z = 1         | BREQ      | Rd ≠ Rr       | Z = 0         | BRNE      | Signed   |

| $Rd \leq Rr$ | Z+(N ⊕ V) = 1 | BRGE*     | Rd > Rr       | Z•(N ⊕ V) = 0 | BRLT*     | Signed   |

| Rd < Rr      | (N ⊕ V) = 1   | BRLT      | Rd ≥ Rr       | (N ⊕ V) = 0   | BRGE      | Signed   |

| Rd > Rr      | C + Z = 0     | BRLO*     | Rd≤Rr         | C + Z = 1     | BRSH*     | Unsigned |

| $Rd \ge Rr$  | C = 0         | BRSH/BRCC | Rd < Rr       | C = 1         | BRLO/BRCS | Unsigned |

| Rd = Rr      | Z = 1         | BREQ      | Rd ≠ Rr       | Z = 0         | BRNE      | Unsigned |

| Rd≤Rr        | C + Z = 1     | BRSH*     | Rd > Rr       | C + Z = 0     | BRLO*     | Unsigned |

| Rd < Rr      | C = 1         | BRLO/BRCS | Rd ≥ Rr       | C = 0         | BRSH/BRCC | Unsigned |

| Carry        | C = 1         | BRCS      | No carry      | C = 0         | BRCC      | Simple   |

| Negative     | N = 1         | BRMI      | Positive      | N = 0         | BRPL      | Simple   |

| Overflow     | V = 1         | BRVS      | No overflow   | V = 0         | BRVC      | Simple   |

| Zero         | Z = 1         | BREQ      | Not zero      | Z = 0         | BRNE      | Simple   |

\* Interchange Rd and Rr in the operation before the test. i.e. CP Rd,  $Rr \rightarrow CP Rr, Rd$

### **Conditional Branch Summary**

### **Complete Instruction Set Summary**

| Mnemonics | Operands    | Description                   | Operation                                                                               | Flags      | #Clock<br>Note |

|-----------|-------------|-------------------------------|-----------------------------------------------------------------------------------------|------------|----------------|

| ARITHMETI | C AND LOGIC | INSTRUCTIONS                  |                                                                                         |            |                |

| ADD       | Rd, Rr      | Add without Carry             | $Rd \gets Rd + Rr$                                                                      | Z,C,N,V,H  | 1              |

| ADC       | Rd, Rr      | Add with Carry                | $Rd \gets Rd + Rr + C$                                                                  | Z,C,N,V,H  | 1              |

| ADIW      | Rd, K       | Add Immediate to Word         | $Rd\text{+1:}Rd \gets Rd\text{+1:}Rd\text{+}K$                                          | Z,C,N,V    | 2              |

| SUB       | Rd, Rr      | Subtract without Carry        | $Rd \gets Rd \text{ - } Rr$                                                             | Z,C,N,V,H  | 1              |

| SUBI      | Rd, K       | Subtract Immediate            | $Rd \gets Rd \textbf{-} K$                                                              | Z,C,N,V,H  | 1              |

| SBC       | Rd, Rr      | Subtract with Carry           | $Rd \gets Rd \text{ - } Rr \text{ - } C$                                                | Z,C,N,V,H  | 1              |

| SBCI      | Rd, K       | Subtract Immediate with Carry | $Rd \gets Rd \textbf{-} K \textbf{-} C$                                                 | Z,C,N,V,H  | 1              |

| SBIW      | Rd, K       | Subtract Immediate from Word  | $Rd\text{+1:}Rd \gets Rd\text{+1:}Rd\text{-}K$                                          | Z,C,N,V    | 2              |

| AND       | Rd, Rr      | Logical AND                   | $Rd \leftarrow Rd$ . $Rr$                                                               | Z,N,V      | 1              |

| ANDI      | Rd, K       | Logical AND with Immediate    | $Rd \gets Rd \boldsymbol{\cdot} K$                                                      | Z,N,V      | 1              |

| OR        | Rd, Rr      | Logical OR                    | $Rd \gets Rd \lor Rr$                                                                   | Z,N,V      | 1              |

| ORI       | Rd, K       | Logical OR with Immediate     | $Rd \gets Rd \lor K$                                                                    | Z,N,V      | 1              |

| EOR       | Rd, Rr      | Exclusive OR                  | $Rd \gets Rd \oplus Rr$                                                                 | Z,N,V      | 1              |

| СОМ       | Rd          | One's Complement              | $Rd \leftarrow \$FF - Rd$                                                               | Z,C,N,V    | 1              |

| NEG       | Rd          | Two's Complement              | Rd ← \$00 - Rd                                                                          | Z,C,N,V,H  | 1              |

| SBR       | Rd,K        | Set Bit(s) in Register        | $Rd \gets Rd \lor K$                                                                    | Z,N,V      | 1              |

| CBR       | Rd,K        | Clear Bit(s) in Register      | $Rd \gets Rd \boldsymbol{\boldsymbol{\cdot}} (\$FFh \boldsymbol{\boldsymbol{\cdot}} K)$ | Z,N,V      | 1              |

| INC       | Rd          | Increment                     | $Rd \gets Rd + 1$                                                                       | Z,N,V      | 1              |

| DEC       | Rd          | Decrement                     | $Rd \leftarrow Rd$ - 1                                                                  | Z,N,V      | 1              |

| TST       | Rd          | Test for Zero or Minus        | $Rd \gets Rd \boldsymbol{\cdot} Rd$                                                     | Z,N,V      | 1              |

| CLR       | Rd          | Clear Register                | $Rd  \leftarrow Rd \oplus Rd$                                                           | Z,N,V      | 1              |

| SER       | Rd          | Set Register                  | $Rd \gets \$FF$                                                                         | None       | 1              |

| СР        | Rd,Rr       | Compare                       | Rd - Rr                                                                                 | Z,C,N,V,H, | 1              |

| CPC       | Rd,Rr       | Compare with Carry            | Rd - Rr - C                                                                             | Z,C,N,V,H  | 1              |

| CPI       | Rd,K        | Compare with Immediate        | Rd - K                                                                                  | Z,C,N,V,H  | 1              |

v) Not available in base-line microcontrollers

(continued)

# **Instruction Set**

### Complete Instruction Set Summary (continued)

| Mnemonics | Operands   | Description                         | Operation                                            | Flags | #Clock<br>Note |

|-----------|------------|-------------------------------------|------------------------------------------------------|-------|----------------|

| BRANCH IN | STRUCTIONS |                                     |                                                      |       |                |

| RJMP      | k          | Relative Jump                       | $PC \leftarrow PC + k + 1$                           | None  | 2              |

| IJMP      |            | Indirect Jump to (Z)                | $PC \leftarrow Z$                                    | None  | 2              |

| JMP       | k          | Jump                                | $PC \leftarrow k$                                    | None  | 3              |

| RCALL     | k          | Relative Call Subroutine            | $PC \leftarrow PC + k + 1$                           | None  | 3              |

| ICALL     |            | Indirect Call to (Z)                | $PC \leftarrow Z$                                    | None  | 3              |

| CALL      | k          | Call Subroutine                     | $PC \leftarrow k$                                    | None  | 4              |

| RET       |            | Subroutine Return                   | $PC \leftarrow STACK$                                | None  | 4              |

| RETI      |            | Interrupt Return                    | $PC \leftarrow STACK$                                | I     | 4              |

| CPSE      | Rd,Rr      | Compare, Skip if Equal              | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3             | None  | 1/2/3          |

| SBRC      | Rr, b      | Skip if Bit in Register Cleared     | if (Rr(b)=0) PC $\leftarrow$ PC + 2 or 3             | None  | 1/2/3          |

| SBRS      | Rr, b      | Skip if Bit in Register Set         | if (Rr(b)=1) PC $\leftarrow$ PC + 2 or 3             | None  | 1/2/3          |

| SBIC      | P, b       | Skip if Bit in I/O Register Cleared | if(I/O(P,b)=0) PC $\leftarrow$ PC + 2 or 3           | None  | 1/2/3          |

| SBIS      | P, b       | Skip if Bit in I/O Register Set     | If(I/O(P,b)=1) PC← PC + 2 or 3                       | None  | 1/2/3          |

| BRBS      | s, k       | Branch if Status Flag Set           | if $(SREG(s) = 1)$ then $PC \leftarrow PC+k + 1$     | None  | 1/2            |

| BRBC      | s, k       | Branch if Status Flag Cleared       | if $(SREG(s) = 0)$ then $PC \leftarrow PC+k + 1$     | None  | 1/2            |

| BREQ      | k          | Branch if Equal                     | if (Z = 1) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRNE      | k          | Branch if Not Equal                 | if (Z = 0) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRCS      | k          | Branch if Carry Set                 | if (C = 1) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRCC      | k          | Branch if Carry Cleared             | if (C = 0) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRSH      | k          | Branch if Same or Higher            | if (C = 0) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRLO      | k          | Branch if Lower                     | if (C = 1) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRMI      | k          | Branch if Minus                     | if (N = 1) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRPL      | k          | Branch if Plus                      | if (N = 0) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRGE      | k          | Branch if Greater or Equal, Signed  | if (N $\oplus$ V= 0) then PC $\leftarrow$ PC+ k + 1  | None  | 1/2            |

| BRLT      | k          | Branch if Less Than, Signed         | if (N $\oplus$ V= 1) then PC $\leftarrow$ PC + k + 1 | None  | 1/2            |

| BRHS      | k          | Branch if Half Carry Flag Set       | if (H = 1) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRHC      | k          | Branch if Half Carry Flag Cleared   | if (H = 0) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRTS      | k          | Branch if T Flag Set                | if (T = 1) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRTC      | k          | Branch if T Flag Cleared            | if (T = 0) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRVS      | k          | Branch if Overflow Flag is Set      | if (V = 1) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRVC      | k          | Branch if Overflow Flag is Cleared  | if (V = 0) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRIE      | k          | Branch if Interrupt Enabled         | if (I = 1) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

| BRID      | k          | Branch if Interrupt Disabled        | if (I = 0) then PC $\leftarrow$ PC + k + 1           | None  | 1/2            |

(continued)

### Complete Instruction Set Summary (continued)

| Mnemonics | Operands     | Description                       | Operation                                              | Flags | #Clock<br>Note |

|-----------|--------------|-----------------------------------|--------------------------------------------------------|-------|----------------|

| DATA TRAN | ISFER INSTRU |                                   |                                                        |       |                |

| MOV       | Rd, Rr       | Copy Register                     | $Rd \leftarrow Rr$                                     | None  | 1              |

| LDI       | Rd, K        | Load Immediate                    | $Rd \leftarrow K$                                      | None  | 1              |

| LDS       | Rd, k        | Load Direct from SRAM             | $Rd \leftarrow (k)$                                    | None  | 3              |

| LD        | Rd, X        | Load Indirect                     | $Rd \leftarrow (X)$                                    | None  | 2              |

| LD        | Rd, X+       | Load Indirect and Post-Increment  | $Rd \leftarrow (X), X \leftarrow X + 1$                | None  | 2              |

| LD        | Rd, -X       | Load Indirect and Pre-Decrement   | $X \leftarrow X - 1, Rd \leftarrow (X)$                | None  | 2              |

| LD        | Rd, Y        | Load Indirect                     | $Rd \leftarrow (Y)$                                    | None  | 2              |

| LD        | Rd, Y+       | Load Indirect and Post-Increment  | $Rd \leftarrow (Y),  Y \leftarrow Y + 1$               | None  | 2              |

| LD        | Rd, -Y       | Load Indirect and Pre-Decrement   | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$                | None  | 2              |

| LDD       | Rd,Y+q       | Load Indirect with Displacement   | $Rd \leftarrow (Y + q)$                                | None  | 2              |

| LD        | Rd, Z        | Load Indirect                     | $Rd \leftarrow (Z)$                                    | None  | 2              |

| LD        | Rd, Z+       | Load Indirect and Post-Increment  | $Rd \leftarrow (Z), Z \leftarrow Z+1$                  | None  | 2              |

| LD        | Rd, -Z       | Load Indirect and Pre-Decrement   | $Z \leftarrow Z - 1, Rd \leftarrow (Z)$                | None  | 2              |

| LDD       | Rd, Z+q      | Load Indirect with Displacement   | $Rd \leftarrow (Z + q)$                                | None  | 2              |

| STS       | k, Rr        | Store Direct to SRAM              | $Rd \leftarrow (k)$                                    | None  | 3              |

| ST        | X, Rr        | Store Indirect                    | $(X) \leftarrow Rr$                                    | None  | 2              |

| ST        | X+, Rr       | Store Indirect and Post-Increment | $(X) \leftarrow \operatorname{Rr}, X \leftarrow X + 1$ | None  | 2              |

| ST        | -X, Rr       | Store Indirect and Pre-Decrement  | $X \leftarrow X - 1, (X) \leftarrow Rr$                | None  | 2              |

| ST        | Y, Rr        | Store Indirect                    | $(Y) \leftarrow Rr$                                    | None  | 2              |

| ST        | Y+, Rr       | Store Indirect and Post-Increment | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$                | None  | 2              |

| ST        | -Y, Rr       | Store Indirect and Pre-Decrement  | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$                | None  | 2              |

| STD       | Y+q,Rr       | Store Indirect with Displacement  | $(Y + q) \leftarrow Rr$                                | None  | 2              |

| ST        | Z, Rr        | Store Indirect                    | $(Z) \leftarrow Rr$                                    | None  | 2              |

| ST        | Z+, Rr       | Store Indirect and Post-Increment | $(Z) \leftarrow Rr, Z \leftarrow Z + 1$                | None  | 2              |

| ST        | -Z, Rr       | Store Indirect and Pre-Decrement  | $Z \leftarrow Z - 1$ , (Z) $\leftarrow Rr$             | None  | 2              |

| STD       | Z+q,Rr       | Store Indirect with Displacement  | $(Z + q) \leftarrow Rr$                                | None  | 2              |

| LPM       |              | Load Program Memory               | $R0 \leftarrow (Z)$                                    | None  | 3              |

| IN        | Rd, P        | In Port                           | $Rd \leftarrow P$                                      | None  | 1              |

| OUT       | P, Rr        | Out Port                          | $P \leftarrow Rr$                                      | None  | 1              |

| PUSH      | Rr           | Push Register on Stack            | $STACK \leftarrow Rr$                                  | None  | 2              |

| POP       | Rd           | Pop Register from Stack           | $Rd \leftarrow STACK$                                  | None  | 2              |

(continued)

# **Instruction Set**

## Complete Instruction Set Summary (continued)

| Mnemonics                     | Operands | Description                     | Operation                                                          | Flags     | #Clock<br>Note |  |

|-------------------------------|----------|---------------------------------|--------------------------------------------------------------------|-----------|----------------|--|

| BIT AND BIT-TEST INSTRUCTIONS |          |                                 |                                                                    |           |                |  |

| LSL                           | Rd       | Logical Shift Left              | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0, C \leftarrow Rd(7)$ | Z,C,N,V,H | 1              |  |

| LSR                           | Rd       | Logical Shift Right             | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0, C \leftarrow Rd(0$  | Z,C,N,V   | 1              |  |

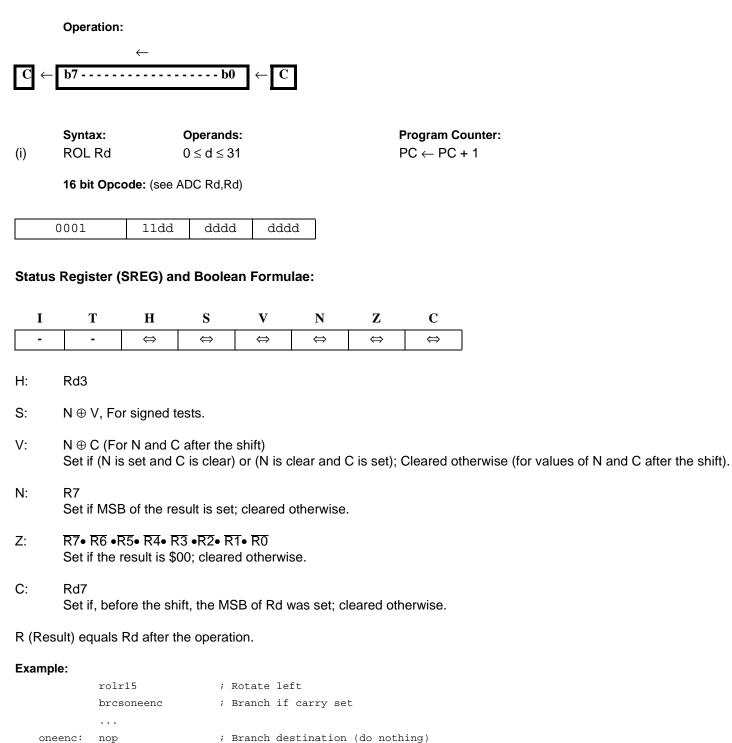

| ROL                           | Rd       | Rotate Left Through Carry       | $Rd(0) \leftarrow C, Rd(n+1) \leftarrow Rd(n), C \leftarrow Rd(7)$ | Z,C,N,V,H | 1              |  |

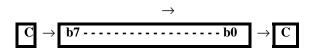

| ROR                           | Rd       | Rotate Right Through Carry      | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0$  | Z,C,N,V   | 1              |  |

| ASR                           | Rd       | Arithmetic Shift Right          | $Rd(n) \leftarrow Rd(n+1), n=06$                                   | Z,C,N,V   | 1              |  |

| SWAP                          | Rd       | Swap Nibbles                    | $Rd(30) \leftrightarrow Rd(74)$                                    | None      | 1              |  |

| BSET                          | s        | Flag Set                        | $SREG(s) \leftarrow 1$                                             | SREG(s)   | 1              |  |

| BCLR                          | S        | Flag Clear                      | $SREG(s) \leftarrow 0$                                             | SREG(s)   | 1              |  |

| SBI                           | P, b     | Set Bit in I/O Register         | I/O(P, b) ← 1                                                      | None      | 2              |  |

| CBI                           | P, b     | Clear Bit in I/O Register       | $I/O(P, b) \leftarrow 0$                                           | None      | 2              |  |

| BST                           | Rr, b    | Bit Store from Register to T    | $T \leftarrow Rr(b)$                                               | Т         | 1              |  |

| BLD                           | Rd, b    | Bit load from T to Register     | $Rd(b) \leftarrow T$                                               | None      | 1              |  |

| SEC                           |          | Set Carry                       | C ← 1                                                              | С         | 1              |  |

| CLC                           |          | Clear Carry                     | $C \leftarrow 0$                                                   | С         | 1              |  |

| SEN                           |          | Set Negative Flag               | N ← 1                                                              | N         | 1              |  |

| CLN                           |          | Clear Negative Flag             | N ← 0                                                              | N         | 1              |  |

| SEZ                           |          | Set Zero Flag                   | Z ← 1                                                              | Z         | 1              |  |

| CLZ                           |          | Clear Zero Flag                 | Z ← 0                                                              | Z         | 1              |  |

| SEI                           |          | Global Interrupt Enable         | I ← 1                                                              | I         | 1              |  |

| CLI                           |          | Global Interrupt Disable        | I ← 0                                                              | 1         | 1              |  |

| SES                           |          | Set Signed Test Flag            | S ← 1                                                              | S         | 1              |  |

| CLS                           |          | Clear Signed Test Flag          | S ← 0                                                              | S         | 1              |  |

| SEV                           |          | Set Two's Complement Overflow   | V ← 1                                                              | V         | 1              |  |

| CLV                           |          | Clear Two's Complement Overflow | $V \leftarrow 0$                                                   | V         | 1              |  |

| SET                           |          | Set T in SREG                   | T ← 1                                                              | Т         | 1              |  |

| CLT                           |          | Clear T in SREG                 | $T \leftarrow 0$                                                   | Т         | 1              |  |

| SEH                           |          | Set Half Carry Flag in SREG     | H ← 1                                                              | Н         | 1              |  |

| CLH                           |          | Clear Half Carry Flag in SREG   | H ← 0                                                              | Н         | 1              |  |

| NOP                           |          | No Operation                    |                                                                    | None      | 1              |  |

| SLEEP                         |          | Sleep                           | (see specific descr. for Sleep)                                    | None      | 1              |  |

| WDR                           |          | Watchdog Reset                  | (see specific descr. for WDR)                                      | None      | 1              |  |

### ADC - Add with Carry

#### **Description:**

Adds two registers and the contents of the C flag and places the result in the destination register Rd.

Operation:

(i)  $Rd \leftarrow Rd + Rr + C$

|     | Syntax:   | Operands:                         |

|-----|-----------|-----------------------------------|

| (i) | ADC Rd,Rr | $0 \le d \le 31,  0 \le r \le 31$ |

Program Counter: PC  $\leftarrow$  PC + 1

16 bit Opcode:

| 0001 | 11rd | dddd | rrrr |

|------|------|------|------|

|      |      |      |      |

### Status Register (SREG) Boolean Formulae:

| Ι | Т | Н                 | S                 | V                 | Ν                 | Z                 | С                 |

|---|---|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| - | - | $\Leftrightarrow$ | $\Leftrightarrow$ | $\Leftrightarrow$ | $\Leftrightarrow$ | $\Leftrightarrow$ | $\Leftrightarrow$ |

- H: Rd3•Rr3+Rr3+R3+R3•Rd3 Set if there was a carry from bit 3; cleared otherwise

- S:  $N \oplus V$ , For signed tests.

- V: Rd7•Rr7•R7+Rd7•Rr7•R7 Set if two's complement overflow resulted from the operation; cleared otherwise.

- N: R7 Set if MSB of the result is set; cleared otherwise.

- Z: Rd7• Rr7• Rr7 R7 R7 R7 Rd7 Set if the result is \$00; cleared otherwise.

- C:  $Rd7 \bullet Rr7 + Rr7 \bullet R7 + R7 \bullet Rd7$ Set if there was carry from the MSB of the result; cleared otherwise.

R (Result) equals Rd after the operation.

#### Example:

; Add R1:R0 to R3:R2 add r2,r0 ; Add low byte adc r3,r1 ; Add with carry high byte

### ADD - Add without Carry

### **Description:**

Adds two registers without the C flag and places the result in the destination register Rd.

|                | Syntax:                                                                                                             |                                                                                                                                                                                                                                                                                    | Operands                                                                                          |                                                    |                                  |                   | Program Co           |             |

|----------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------|-------------------|----------------------|-------------|

|                | ADD Rd,R                                                                                                            | tr                                                                                                                                                                                                                                                                                 | $0 \le d \le 3$                                                                                   | 1, 0 ≤ r ≤                                         | 31                               |                   | $PC \leftarrow PC +$ | • 1         |

|                | 16 bit Opco                                                                                                         | ode:                                                                                                                                                                                                                                                                               |                                                                                                   |                                                    |                                  |                   |                      |             |

|                | 0000                                                                                                                | 11rd                                                                                                                                                                                                                                                                               | dddd                                                                                              | l rri                                              | rr                               |                   |                      |             |

|                |                                                                                                                     |                                                                                                                                                                                                                                                                                    |                                                                                                   | _                                                  | _                                |                   |                      |             |

| tatus          | s Register (                                                                                                        | SREG) an                                                                                                                                                                                                                                                                           | d Boolea                                                                                          | an Formu                                           | ilae:                            |                   |                      |             |

| Ι              | Т                                                                                                                   | Н                                                                                                                                                                                                                                                                                  | S                                                                                                 | V                                                  | Ν                                | Z                 | С                    |             |

| -              | -                                                                                                                   | $\Leftrightarrow$                                                                                                                                                                                                                                                                  | $\Leftrightarrow$                                                                                 | $\Leftrightarrow$                                  | ⇔                                | $\Leftrightarrow$ | $\Leftrightarrow$    |             |

| -              | Set if there                                                                                                        | Rr3+ <del>R3</del> +F<br>e was a ca                                                                                                                                                                                                                                                |                                                                                                   | bit 3; clea                                        | ared other                       | wise              |                      |             |

| l:<br>;:<br>': | Set if there<br>N ⊕ V, For<br>Rd7•Rr7•I                                                                             | e was a ca<br>r signed te<br>R7+Rd7∙R                                                                                                                                                                                                                                              | erry from l<br>ests.<br>Rr <b>7</b> •R7                                                           |                                                    |                                  |                   | ion; clearec         | d otherwise |

| ):<br>-        | Set if there<br>N ⊕ V, For<br>Rd7•Rr7•I                                                                             | e was a ca<br>r signed te<br>R7+Rd7∙R<br>s complem                                                                                                                                                                                                                                 | nry from l<br>ests.<br>Rr7∙R7<br>nent overl                                                       | flow resu                                          | Ited from t                      | he operat         | ion; cleared         | d otherwise |

| 5:<br>7:       | Set if there<br>N ⊕ V, Fot<br>Rd7∙Rr7•I<br>Set if two's<br>R7                                                       | e was a ca<br>r signed te<br>R7+Rd7•R<br>s complem<br>3 of the res<br>R5• R4 •R3                                                                                                                                                                                                   | arry from I<br>ests.<br>Rr7•R7<br>hent overf<br>sult is set<br>3 •R2 •R                           | flow resul<br>; cleared<br>1 ∙R0                   | lted from t<br>otherwise         | he operat         | ion; clearec         | d otherwise |

| :              | Set if there<br>N ⊕ V, For<br>Rd7•Rr7•<br>Set if two's<br>R7<br>Set if MSE<br>R7• R6 •R<br>Set if the r<br>Rd7 •Rr7 | e was a ca<br>r signed te<br>R7+Rd7•R<br>s complem<br>3 of the res<br>8 of the res<br>8 of the res<br>8 of the res<br>9 of the res<br>8 of the res<br>9 of the res | arry from l<br>asts.<br>Ar7∙R7<br>hent overl<br>sult is set<br>3 •R2 •R<br>10; cleare<br>+ R7 •Rd | flow resul<br>; cleared<br>1 ∙R0<br>d otherwi<br>7 | Ited from t<br>otherwise<br>ise. | he operat         | ion; clearec         | d otherwise |

add r1,r2 ; Add r2 to r1 (r1=r1+r2) add r28,r28 ; Add r28 to itself (r28=r28+r28)

### ADIW - Add Immediate to Word

#### **Description:**

Adds an immediate value (0-63) to a register pair and places the result in the register pair. This instruction operates on the upper four register pairs, and is well suited for operations on the pointer registers.

| -     |         |    |

|-------|---------|----|

| - ( ) | peratic | ۱n |

|       | peratic |    |

(i)  $Rdh:RdI \leftarrow Rdh:RdI + K$

|     | Syntax:    | Operands:                                         | Program Counter:  |

|-----|------------|---------------------------------------------------|-------------------|

| (i) | ADIW Rdl,K | $dI \in \ \{24, 26, 28, 30\}, \ 0 \leq K \leq 63$ | $PC \gets PC + 1$ |

16 bit Opcode:

| 1001 | 0110 | KKdd | KKKK |

|------|------|------|------|

|------|------|------|------|

#### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S                 | V                 | Ν                 | Ζ                 | С                 |

|---|---|---|-------------------|-------------------|-------------------|-------------------|-------------------|

| - | - | - | $\Leftrightarrow$ | $\Leftrightarrow$ | $\Leftrightarrow$ | $\Leftrightarrow$ | $\Leftrightarrow$ |

- S:  $N \oplus V$ , For signed tests.

- V: Rdh7 R15 Set if two's complement overflow resulted from the operation; cleared otherwise.

- N: R15

Set if MSB of the result is set; cleared otherwise.

- Z: R15 •R14 •R13 •R12 •R11 •R10 •R9 •R8 •R7• R6• R5• R4• R3• R2 •R1• R0 Set if the result is \$0000; cleared otherwise.

- C:  $\overline{R15} \bullet Rdh7$ Set if there was carry from the MSB of the result; cleared otherwise.

- R (Result) equals Rdh:Rdl after the operation (Rdh7-Rdh0 = R15-R8, Rdl7-Rdl0=R7-R0).

#### Example:

adiw r24,1 ; Add 1 to r25:r24 adiw r30,63 ; Add 63 to the Z pointer(r31:r30)

Words: 1 (2 bytes) Cycles: 2

# 6-8 Instruction Set

**Instruction Set**

### **AND - Logical AND**

### **Description:**

Performs the logical AND between the contents of register Rd and register Rr and places the result in the destination register Rd.

| Operation: |

|------------|

|------------|

(i)  $Rd \leftarrow Rd \bullet Rr$

|     | Syntax:   | Operands:                        |

|-----|-----------|----------------------------------|

| (i) | AND Rd,Rr | $0 \le d \le 31, 0 \le r \le 31$ |

Program Counter: PC  $\leftarrow$  PC + 1

#### 16 bit Opcode:

| 0010 | 00rd | dddd | rrrr |

|------|------|------|------|

| 0010 | UULU | uuuu |      |

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Η | S | V | Ν | Ζ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | ⇔ | 0 | ⇔ | ⇔ | - |

- S:  $N \oplus V$ , For signed tests.

- V: 0

Cleared

- N: R7 Set if MSB of the result is set; cleared otherwise.

- Z: R7 •R6 •R5 •R4 •R3• R2 •R1 •R0 Set if the result is \$00; cleared otherwise.

R (Result) equals Rd after the operation.

#### Example:

| and r2,r3  | ; Bitwise and r2 and r3, result in r2 |

|------------|---------------------------------------|

| ldi r16,1  | ; Set bitmask 0000 0001 in r16        |

| and r2,r16 | ; Isolate bit 0 in r2                 |

### **ANDI - Logical AND with Immediate**

### **Description:**

Performs the logical AND between the contents of register Rd and a constant and places the result in the destination register Rd.

| Operation: |

|------------|

|------------|

(i)  $Rd \leftarrow Rd \bullet K$

|     | Syntax:   | Operands:                               |

|-----|-----------|-----------------------------------------|

| (i) | ANDI Rd,K | $16 \leq d \leq 31,  0 \leq K \leq 255$ |

Program Counter: PC  $\leftarrow$  PC + 1

16 bit Opcode:

| 0111 KKKK dddd |

|----------------|

|----------------|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S | V | Ν | Z | С |

|---|---|---|---|---|---|---|---|

| - | - | - | ⇔ | 0 | ⇔ | ⇔ | - |

- S:  $N \oplus V$ , For signed tests.

- V: 0

Cleared

- N: R7 Set if MSB of the result is set; cleared otherwise.

- Z: R7 •R6• R5•R4 •R3• R2• R1• R0 Set if the result is \$00; cleared otherwise.

R (Result) equals Rd after the operation.

### Example:

| andi r17,\$0F | ; Clear upper nibble of r17 |

|---------------|-----------------------------|

| andi r18,\$10 | ; Isolate bit 4 in r18      |

| andi r19,\$AA | ; Clear odd bits of r19     |

### Words: 1 (2 bytes)

Cycles: 1

**Instruction Set**

### **ASR - Arithmetic Shift Right**

### **Description:**

Shifts all bits in Rd one place to the right. Bit 7 is held constant. Bit 0 is loaded into the C flag of the SREG. This operation effectively divides a twos complement value by two without changing its sign. The carry flag can be used to round the result.

|     | Operation:     |                  |                   |

|-----|----------------|------------------|-------------------|

| (i) |                |                  |                   |

| Ţ   | b7             | →<br>- b0 C      |                   |

|     | Syntax:        | Operands:        | Program Counter:  |

| (i) | ASR Rd         | $0 \le d \le 31$ | $PC \gets PC + 1$ |

|     | 16 bit Opcode: |                  |                   |

0101

### Status Register (SREG) and Boolean Formulae:

010d

| Ι | Т | н | S | $\mathbf{V}$ | Ν | Z | С |

|---|---|---|---|--------------|---|---|---|

| - | - | - | ⇔ | ⇔            | ⇔ | ⇔ | ⇔ |

dddd

S:  $N \oplus V$ , For signed tests.

1001

- V: N ⊕ C (For N and C after the shift)

Set if (N is set and C is clear) or (N is clear and C is set); Cleared otherwise (for values of N and C after the shift).

- N: R7 Set if MSB of the result is set; cleared otherwise.

- Z: R7 •R6 •R5• R4 •R3 •R2• R1• R0 Set if the result is \$00; cleared otherwise.

- C: Rd0 Set if, before the shift, the LSB of Rd was set; cleared otherwise.

R (Result) equals Rd after the operation.

#### Example:

ldi

r16,\$10

; Load decimal 16 into r16

asr

r16

; r16=r16 / 2

ldi

r17,\$FC

; Load -4 in r17

asr

r17

; r17=r17/2

### BCLR - Bit Clear in SREG

### **Description:**

Clears a single flag in SREG.

### **Operation:**

- (i)  $SREG(s) \leftarrow 0$

- Syntax:Operands:Program Counter:(i)BCLR s $0 \le s \le 7$ PC  $\leftarrow$  PC + 1

#### 16 bit Opcode:

| 1001 | 0100 | lsss | 1000 |

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

| Ι                 | Т                 | Н | S                 | V                 | Ν                 | Ζ                 | С                 |

|-------------------|-------------------|---|-------------------|-------------------|-------------------|-------------------|-------------------|

| $\Leftrightarrow$ | $\Leftrightarrow$ | ⇔ | $\Leftrightarrow$ | $\Leftrightarrow$ | $\Leftrightarrow$ | $\Leftrightarrow$ | $\Leftrightarrow$ |

- I: 0 if s = 7; Unchanged otherwise.

- T: 0 if s = 6; Unchanged otherwise.

- H: 0 if s = 5; Unchanged otherwise.

- S: 0 if s = 4; Unchanged otherwise.

- V: 0 if s = 3; Unchanged otherwise.

- N: 0 if s = 2; Unchanged otherwise.

- Z: 0 if s = 1; Unchanged otherwise.

- C: 0 if s = 0; Unchanged otherwise.

#### Example:

| bclr | 0 | ; Clear carry flag   |

|------|---|----------------------|

| bclr | 7 | ; Disable interrupts |

### BLD - Bit Load from the T Flag in SREG to a Bit in Register.

### **Description:**

Copies the T flag in the SREG (status register) to bit b in register Rd.

### Operation:

(i)  $Rd(b) \leftarrow T$

|     | Syntax:  | Operands:                      | Program Counter:  |

|-----|----------|--------------------------------|-------------------|

| (i) | BLD Rd,b | $0\leq d\leq 31,0\leq b\leq 7$ | $PC \gets PC + 1$ |

16 bit Opcode:

| 1111 100d dddd |

|----------------|

|----------------|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S | V | Ν | Ζ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

### Example:

|     |      | ; | Copy bit                     |

|-----|------|---|------------------------------|

| bst | r1,2 | ; | Store bit 2 of r1 in T flag  |

| bld | r0,4 | ; | Load T flag into bit 4 of r0 |

### **BRBC - Branch if Bit in SREG is Cleared**

### **Description:**

Conditional relative branch. Tests a single bit in SREG and branches relatively to PC if the bit is cleared. This instruction branches relatively to PC in either direction (PC-64≤destination≤PC+63). The parameter k is the offset from PC and is represented in two's complement form.

### **Operation:**

(i) If SREG(s) = 0 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax:  | Operands:                | Program Counter:                               |

|-----|----------|--------------------------|------------------------------------------------|

| (i) | BRBC s,k | 0 ≤ s ≤ 7, -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |          |                          | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

|--|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S | V | Ν | Ζ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

#### Example:

cpi r20,5 ; Compare r20 to the value 5

brbc 1,noteq ; Branch if zero flag cleared

...

noteq:nop ; Branch destination (do nothing)

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRBS - Branch if Bit in SREG is Set**

### **Description:**

Conditional relative branch. Tests a single bit in SREG and branches relatively to PC if the bit is set. This instruction branches relatively to PC in either direction (PC-64≤destination≤PC+63). The parameter k is the offset from PC and is represented in two's complement form.

### **Operation:**

(i) If SREG(s) = 1 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax:  | Operands:                | Program Counter:                               |

|-----|----------|--------------------------|------------------------------------------------|

| (i) | BRBS s,k | 0 ≤ s ≤ 7, -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |          |                          | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 00kk | kkkk | ksss |

|------|------|------|------|

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S | V | Ν | Ζ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

#### Example:

bst r0,3 ; Load T bit with bit 3 of r0 brbs 6,bitset ; Branch T bit was set ... bitset: nop ; Branch destination (do nothing)

#### Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRCC - Branch if Carry Cleared**

### **Description:**

Conditional relative branch. Tests the Carry flag (C) and branches relatively to PC if C is cleared. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBC 0,k).

### **Operation:**

(i) If C = 0 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRCC k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 01kk | kkkk | k000 | 1 |

|------|------|------|------|---|

|------|------|------|------|---|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S | V | Ν | Z | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

#### Example:

addr22,r23 ; Add r23 to r22 brccnocarry ; Branch if carry cleared ... nocarry: nop ; Branch destination (do nothing)

### Words: 1 (2 bytes)

- Cycles: 1 if condition is false

- 2 if condition is true

### **BRCS - Branch if Carry Set**

### **Description:**

Conditional relative branch. Tests the Carry flag (C) and branches relatively to PC if C is set. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBS 0,k).

### **Operation:**

(i) If C = 1 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRCS k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 00kk | kkkk | k000 |

|------|------|------|------|

|      |      |      |      |

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Η | S | V | Ν | Ζ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

#### Example:

cpi r26,\$56 ; Compare r26 with \$56

brcs carry ; Branch if carry set

...

carry: nop ; Branch destination (do nothing)

### Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BREQ - Branch if Equal**

#### **Description:**

Conditional relative branch. Tests the Zero flag (Z) and branches relatively to PC if Z is set. If the instruction is executed immediately after any of the instructions CP, CPI, SUB or SUBI, the branch will occur if and only if the unsigned or signed binary number represented in Rd was equal to the unsigned or signed binary number represented in Rr. This instruction branches relatively to PC in either direction (PC-64≤destination≤PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBS 1,k).

Operation:

(i) If Rd = Rr (Z = 1) then  $PC \leftarrow PC + k + 1$ , else  $PC \leftarrow PC + 1$

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BREQ k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 00kk | kkkk | k001 |

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

| Ι                                                 | Т             | Н | S                           | V         | Ν         | Ζ    | С |

|---------------------------------------------------|---------------|---|-----------------------------|-----------|-----------|------|---|

| -                                                 | -             | - | -                           | -         | -         | -    | - |

| Example:<br>cpr1,r0 ; Compare registers r1 and r0 |               |   |                             |           |           |      |   |

|                                                   | breqe         |   | ; Branch if registers equal |           |           |      |   |

| equal                                             | ••••<br>• nop | ; | Branch de                   | stination | (do nothi | ing) |   |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRGE - Branch if Greater or Equal (Signed)**

### Description:

Conditional relative branch. Tests the Signed flag (S) and branches relatively to PC if S is cleared. If the instruction is executed immediately after any of the instructions CP, CPI, SUB or SUBI, the branch will occur if and only if the signed binary number represented in Rd was greater than or equal to the signed binary number represented in Rr. This instruction branches relatively to PC in either direction (PC-64≤destination≤PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBC 4,k).

**Operation:**

(i) If  $Rd \ge Rr (N \oplus V = 0)$  then  $PC \leftarrow PC + k + 1$ , else  $PC \leftarrow PC + 1$

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRGE k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 01kk | kkkk | k100 |

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

|     | I     | Т            | Н                  | S        | V                        | Ν         | Z       | С |

|-----|-------|--------------|--------------------|----------|--------------------------|-----------|---------|---|

|     | -     | -            | -                  | -        | -                        | -         | -       | - |

| Exa | mple: | cpr          | 11,r12<br>egreateq | -        | re registe<br>1 if rll > |           |         |   |

|     | great | <br>Leq: nop |                    | ; Branch | destinat                 | ion (do r | othing) |   |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRHC - Branch if Half Carry Flag is Cleared**

### **Description:**

Conditional relative branch. Tests the Half Carry flag (H) and branches relatively to PC if H is cleared. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBC 5,k).

### **Operation:**

(i) If H = 0 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRHC k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 01kk kkkk k101 |      |      |      |      |

|---------------------|------|------|------|------|

|                     | 1111 | 01kk | kkkk | k101 |

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Η | S | V | Ν | Z | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

#### Example:

|         | brhc hclear | ; Branch if half carry flag cleared |

|---------|-------------|-------------------------------------|

|         |             |                                     |

| hclear: | nop         | ; Branch destination (do nothing)   |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRHS - Branch if Half Carry Flag is Set**

### **Description:**

Conditional relative branch. Tests the Half Carry flag (H) and branches relatively to PC if H is set. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBS 5,k).

### **Operation:**

(i) If H = 1 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRHS k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

|--|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S | V | Ν | Ζ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

### Example:

|       | brhshset | ; | Branch | if | half   | carr | y f | lag | set   |

|-------|----------|---|--------|----|--------|------|-----|-----|-------|

|       |          |   |        |    |        |      |     |     |       |

| hset: | nop      | ; | Branch | de | stinat | cion | (do | not | hing) |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRID - Branch if Global Interrupt is Disabled**

### **Description:**

Conditional relative branch. Tests the Global Interrupt flag (I) and branches relatively to PC if I is cleared. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBC 7,k).

#### **Operation:**

(i) If I = 0 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRID k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

|--|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S | $\mathbf{V}$ | Ν | Ζ | С |

|---|---|---|---|--------------|---|---|---|

| - | - | - | - | -            | - | - | - |

#### Example:

|         | brid intdis | ; | Branch | if  | interrupt | di  | sabled   |

|---------|-------------|---|--------|-----|-----------|-----|----------|

|         |             |   |        |     |           |     |          |

| intdis: | nop         | ; | Branch | des | stination | (do | nothing) |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRIE - Branch if Global Interrupt is Enabled**

### **Description:**

Conditional relative branch. Tests the Global Interrupt flag (I) and branches relatively to PC if I is set. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBS 7,k).

### **Operation:**

(i) If I = 1 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRIE k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 00kk | kkkk | k111 |

|------|------|------|------|

|      |      |      |      |

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Η | S | V | Ν | Z | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

#### Example:

|        | brieinten | ; | Branch | if  | interrupt | ena | abled    |

|--------|-----------|---|--------|-----|-----------|-----|----------|

|        |           |   |        |     |           |     |          |

| inten: | nop       | ; | Branch | des | stination | (do | nothing) |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

# AIMEL

### **BRLO - Branch if Lower (Unsigned)**

### Description:

Conditional relative branch. Tests the Carry flag (C) and branches relatively to PC if C is set. If the instruction is executed immediately after any of the instructions CP, CPI, SUB or SUBI, the branch will occur if and only if the unsigned binary number represented in Rd was smaller than the unsigned binary number represented in Rr. This instruction branches relatively to PC in either direction (PC-64≤destination≤PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBS 0,k).

#### Operation:

(i) If Rd < Rr (C = 1) then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRLO k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 00kk | kkkk | k000 |

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Η | S | V | Ν | Z | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

### Example:

|       | eor  | r19,r19  | ; Clear r19                       |

|-------|------|----------|-----------------------------------|

| loop: | inc  | r19      | ; Increase r19                    |

|       |      |          |                                   |

|       | cpi  | r19,\$10 | ; Compare r19 with \$10           |

|       | brlo | loop     | ; Branch if r19 < \$10 (unsigned) |

|       | nop  |          | ; Exit from loop (do nothing)     |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRLT - Branch if Less Than (Signed)**

### **Description:**

Conditional relative branch. Tests the Signed flag (S) and branches relatively to PC if S is set. If the instruction is executed immediately after any of the instructions CP, CPI, SUB or SUBI, the branch will occur if and only if the signed binary number represented in Rd was less than the signed binary number represented in Rr. This instruction branches relatively to PC in either direction (PC-64≤destination≤PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBS 4,k).

**Operation:**

(i) If Rd < Rr (N  $\oplus$  V = 1) then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRLT k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 00kk | kkkk | k100 |

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S | V | Ν | Ζ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Example:

|       | cp    | r16,r1 | ; | Compare r16 to r1               |

|-------|-------|--------|---|---------------------------------|

|       | brlt  | less   | ; | Branch if rl6 < rl (signed)     |

|       | • • • |        |   |                                 |

| less: | nop   |        | ; | Branch destination (do nothing) |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRMI - Branch if Minus**

### **Description:**

Conditional relative branch. Tests the Negative flag (N) and branches relatively to PC if N is set. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBS 2,k).

### **Operation:**

(i) If N = 1 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRMI k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 00kk | kkkk | k010 |

|------|------|------|------|

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S | V | Ν | Ζ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

#### Example:

|           | subi | r18,4    | ; Subtract 4 from r18             |

|-----------|------|----------|-----------------------------------|

|           | brmi | negative | ; Branch if result negative       |

|           | •••  |          |                                   |

| negative: | nop  |          | ; Branch destination (do nothing) |

### Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRNE - Branch if Not Equal**

### **Description:**

Conditional relative branch. Tests the Zero flag (Z) and branches relatively to PC if Z is cleared. If the instruction is executed immediately after any of the instructions CP, CPI, SUB or SUBI, the branch will occur if and only if the unsigned or signed binary number represented in Rd was not equal to the unsigned or signed binary number represented in Rr. This instruction branches relatively to PC in either direction (PC-64≤destination≤PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBC 1,k).

#### Operation:

(i) If  $Rd \neq Rr (Z = 0)$  then  $PC \leftarrow PC + k + 1$ , else  $PC \leftarrow PC + 1$

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRNE k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

#### 16 bit Opcode:

| 1111 | 01kk | kkkk | k001 |

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

| Ι       | Т | Н | S | V | Ν | Ζ | С |

|---------|---|---|---|---|---|---|---|

| -       | - | - | - | - | - | - | - |

|         |   |   |   |   |   |   |   |

| Example | : |   |   |   |   |   |   |

|       | eor  | r27,r27 | ; Clear r27              |

|-------|------|---------|--------------------------|

| loop: | inc  | r27     | ; Increase r27           |

|       |      |         |                          |

|       | cpi  | r27,5   | ; Compare r27 to 5       |

|       | brne | loop    | ; Branch if r27<>5       |

|       | nop  |         | ; Loop exit (do nothing) |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRPL** - Branch if Plus

### **Description:**

Conditional relative branch. Tests the Negative flag (N) and branches relatively to PC if N is cleared. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBC 2,k).

### **Operation:**

(i) If N = 0 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRPL k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| IIII UIKK KKKK KUIU |

|---------------------|

|---------------------|

### Status Register (SREG) and Boolean Formulae:

| _   | Ι     | Т     | Η                  | S | V      | Ν                       | Ζ         | С           |

|-----|-------|-------|--------------------|---|--------|-------------------------|-----------|-------------|

|     | -     | -     | -                  | - | -      | -                       | -         | -           |

| Exa | ample | :     | subi r2<br>brpl po |   |        | ract \$50<br>nch if r26 |           |             |

|     | posi  | tive: | nop                |   | ; Brar | nch destir              | nation (d | lo nothing) |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRSH - Branch if Same or Higher (Unsigned)**

### **Description:**

Conditional relative branch. Tests the Carry flag (C) and branches relatively to PC if C is cleared. If the instruction is executed immediately after execution of any of the instructions CP, CPI, SUB or SUBI the branch will occur if and only if the unsigned binary number represented in Rd was greater than or equal to the unsigned binary number represented in Rr. This instruction branches relatively to PC in either direction (PC-64≤destination≤PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBC 0,k).

Operation:

(i) If  $Rd \ge Rr (C = 0)$  then  $PC \leftarrow PC + k + 1$ , else  $PC \leftarrow PC + 1$

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRSH k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

; Branch destination (do nothing)

16 bit Opcode:

| 1111 | 01kk | kkkk | k000 |

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

| Ι                                | Т | ТН        |    | V        | V N       |          | С    |  |  |  |

|----------------------------------|---|-----------|----|----------|-----------|----------|------|--|--|--|

| -                                | - | -         | -  | -        | -         | -        | -    |  |  |  |

| Example:                         |   |           |    |          |           |          |      |  |  |  |

| subi r19,4 ; Subtract 4 from r19 |   |           |    |          |           |          |      |  |  |  |

|                                  | b | rsh highs | sm | Branch : | if r19 >= | 4 (unsig | ned) |  |  |  |

Words: 1 (2 bytes)

highsm:

Cycles: 1 if condition is false

2 if condition is true

. . .

nop

### BRTC - Branch if the T Flag is Cleared

### **Description:**

Conditional relative branch. Tests the T flag and branches relatively to PC if T is cleared. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBC 6,k).

### **Operation:**

(i) If T = 0 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRTC k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 01kk kkkk k110 |

|---------------------|

|---------------------|

### Status Register (SREG) and Boolean Formulae:

| - | Ι       | Т | Η     | S   | V         | Ν       | Ζ         | С |

|---|---------|---|-------|-----|-----------|---------|-----------|---|

|   | -       | - | -     | -   | -         | -       | -         | - |

|   | Example |   | at r3 | 5 : | Store bit | 5 of r3 | in T flag |   |

|         | bst  | r3,5   | ; | Store 1 | oit | 5 OI   | r3 : | ın T | ilag     |

|---------|------|--------|---|---------|-----|--------|------|------|----------|

|         | brtc | tclear | ; | Branch  | if  | this   | bit  | was  | cleared  |

|         | •••  |        |   |         |     |        |      |      |          |

| tclear: | nop  |        | ; | Branch  | des | stinat | cion | (do  | nothing) |

Words: 1 (2 bytes)

Cycles: 1 if condition is false

### BRTS - Branch if the T Flag is Set

### **Description:**

Conditional relative branch. Tests the T flag and branches relatively to PC if T is set. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBS 6,k).

### **Operation:**

(i) If T = 1 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRTS k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 00kk | kkkk | k110 |

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Н | S | V | Ν | Ζ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

#### Example:

|       | bst  | r3,5 | ; | Store bi | it 5 | of   | r3 : | in T | flag     |

|-------|------|------|---|----------|------|------|------|------|----------|

|       | brts | tset | ; | Branch i | if t | his  | bit  | was  | set      |

|       | •••  |      |   |          |      |      |      |      |          |

| tset: | nop  |      | ; | Branch d | dest | inat | ion  | (do  | nothing) |

### Words: 1 (2 bytes)

- Cycles: 1 if condition is false

- 2 if condition is true

### **BRVC - Branch if Overflow Cleared**

### **Description:**

Conditional relative branch. Tests the Overflow flag (V) and branches relatively to PC if V is cleared. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBC 3,k).

### **Operation:**

(i) If V = 0 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRVC k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 01kk | kkkk | k011 |

|------|------|------|------|

#### Status Register (SREG) and Boolean Formulae:

| Ι | Т | Η | S | V | Ν | Ζ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

#### Example:

|         | add   | r3,r4  | ; | Add r4 | to r3 |        |     |          |

|---------|-------|--------|---|--------|-------|--------|-----|----------|

|         | brvc  | noover | ; | Branch | if no | overfl | .ow |          |

|         | • • • |        |   |        |       |        |     |          |

| noover: | nop   |        | ; | Branch | desti | nation | (do | nothing) |

#### Words: 1 (2 bytes)

Cycles: 1 if condition is false

### **BRVS - Branch if Overflow Set**

### **Description:**

Conditional relative branch. Tests the Overflow flag (V) and branches relatively to PC if V is set. This instruction branches relatively to PC in either direction (PC-64 $\leq$ destination $\leq$ PC+63). The parameter k is the offset from PC and is represented in two's complement form. (Equivalent to instruction BRBS 3,k).

### **Operation:**

(i) If V = 1 then PC  $\leftarrow$  PC + k + 1, else PC  $\leftarrow$  PC + 1

|     | Syntax: | Operands:     | Program Counter:                               |

|-----|---------|---------------|------------------------------------------------|

| (i) | BRVS k  | -64 ≤ k ≤ +63 | $PC \leftarrow PC + k + 1$                     |

|     |         |               | $PC \leftarrow PC + 1$ , if condition is false |

16 bit Opcode:

| 1111 | 00kk | kkkk | k011 |

|------|------|------|------|

|------|------|------|------|

### Status Register (SREG) and Boolean Formulae:

| Ι       | Т | Н       | S    | V        | Ν          | Ζ        | С      |

|---------|---|---------|------|----------|------------|----------|--------|

| -       | - | -       | -    | -        | -          | -        | -      |

| Example |   | add r3. | r4 ; | ; Add r4 | to r3      |          |        |

|         |   |         |      |          | if overflo | W        |        |

| over    |   | nop     | į    | ; Branch | destinatio | n (do no | thing) |

- Words: 1 (2 bytes)

- Cycles: 1 if condition is false

### **BSET - Bit Set in SREG**

### **Description:**

Sets a single flag or bit in SREG.

### Operation: